# EXPERIMENT #5 MOSFET MEASUREMENT and APPLICATIONS

### I OBJECTIVES

The overall objective of this Experiment is to familiarize you, the experimenter, with some of the basic properties of MOS transistors, both n and p channel, and to begin the exploration of some of their fundamental applications.

# II COMPONENTS AND INSTRUMENTATION

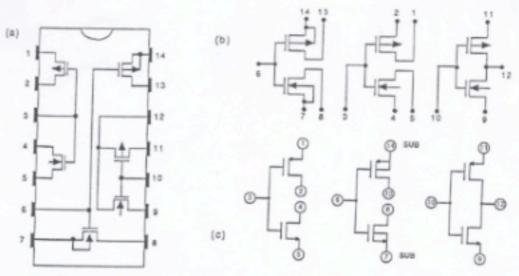

Our concentration will be on the 4007 MOS array whose package, layout and connections are shown in Fig. 5.1. As can be seen, the array consists of 6 transistors, 3 p-channel and 3 n-channel, interconnected to some extent in order to reduce the number of IC pins required, but otherwise fairly flexible. One critical point to note is that pins 14 and 7, being the substrate connections of all of the p-channel and all of the n-channel devices, respectively, must be connected appropriately, no matter what use is made of any device. In particular, pin 14 must be connected to the most positive supply in use, and pin 7 to the most negative. Note also that the voltage between pin 14 and pin 7, must be limited to 18 V or so, otherwise internal voltage breakdown may result. For safety's sake, maintain this total supply value at or below 16 V.

Other components necessary include resistors of various "unit" values, and a 0.1µF capacitor, in addition to power-supply filters<sup>1</sup> A second 4007, if available, can be used to evaluate IC-to-IC device variability as an optional exercise.

Instrumentation necessary includes a general-purpose DMM, a dual power supply, a waveform generator and a dual-channel oscilloscope with ×10 probes. A characteristic-curve tracer would be useful, although not essential.

Figure 5.1 The 4007 MOS Array: a) Base Diagram, top view; b) Pin Assignment, substrateoriented symbols; c) Pin Assignment, simplified

<sup>5</sup> See the "Survival Tips" at the end of the Preface, Experiment #0, and Appendix B10.

### III READING

The background for this Experiment can be found in Sections 5.1, 5.2, 5.4, 5.5 and 5.6 of the Text.

### IV PREPARATION

Following the usual pattern in this Manual, Preparation tasks are keyed directly to the Explorations to follow, through the use of the same section numbering and titling, but with a P prefix.

### DEVICE-INTEGRITY CHECKING

### P1.1 Measuring Device Thresholds

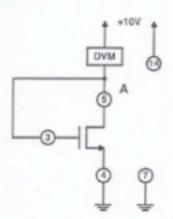

(a) For the setup shown in Fig. 5.2, with the supply voltage adjusted to 10.00 V, the DVM reading (node A to ground) is found to be 8.91 V. Estimate the device-threshold magnitude.

# P1.2 Measuring the Device Conductivity Parameter

(a) For the setup shown in Fig. 5.2, and the device and situation described in P1.1(a) above, a 1kΩ resistor shunting the DVM reduces its reading to 1.53 V. What value of k<sub>n</sub> = μ<sub>n</sub>C<sub>ex</sub>(W/L)<sub>n</sub> applies?

### THE AMPLIFIER FUNCTION

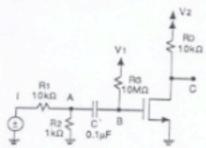

(a) For a transistor for which V<sub>t</sub> = 0.90 V, k<sub>z</sub> = μ<sub>z</sub> C<sub>ex</sub> (W/L)<sub>z</sub> = 0.6mA/V<sup>2</sup>, in the circuit of Fig. 5.4, calculate the values of V<sub>1</sub> and V<sub>2</sub> required to provide i<sub>D</sub> = 0.1mA with v<sub>OS</sub> = 5 V.

### P2.1 Device Transconductance

(a) For the situation in (a) jsut above, calculate the value of g<sub>w</sub> you can expect. For the 10 kΩ drain resistor, what voltage gain would you get? For a sinewave signal at node I of I Vpp, what signal would you expect at node C?

## THE FEEDBACK-BIAS TOPOLOGY

# P3.1 A CMOS Active-Loaded Amplifier

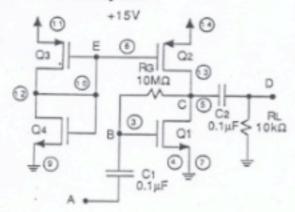

- (a) For the circuit of Fig. 5.5, in which |V<sub>t</sub>| = 1.0 V and k = 0.6 mA/V<sup>2</sup>, find the device drain currents which result, and V<sub>C</sub>.

- (b) For V<sub>A</sub> = 30 V, find g<sub>m</sub>, r<sub>e</sub> and gain υ<sub>θ</sub>/υ<sub>e</sub>.

- (c) For what peak output and input signals are the output transistors still in saturation?

### P3.3 Measuring the Input Resistance

- (a) For the situation described in P3.1(a), estimate the input resistance seen to the right of node B. Use the fact (called Miller multiplication) that, for a resistor R connected from output to input of an amplifier of gain A, the corresponding input resistance is R / (1 − A).

- (b) For a signal supplied from node I to node A through a 1 MΩ resistor, what is the gain v<sub>d</sub> / v<sub>l</sub> which results?

### V EXPLORATIONS

### DEVICE-INTEGRITY CHECKING

The purpose of the two Explorations to follow is to introduce techniques for the rapid evaluation of devices in your MOS array. While you may find the ideas involved not directly obvious at first, depending of course on how much and how thoroughly you have read and understood the Text, the basic underlying process is experimentally very simple, and will become clearer as you proceed. What is most important is that you will practice evaluation techniques which will serve you well later when something does not work as expected, and you wish to verify that your IC still functions.

# E1.1 Measuring Device Thresholds

### · Goal:

To experience, at first hand, how much useful information can be extracted from a simple experiment (in conjunction with E1.2 to follow); Specifically, here, to find  $V_I$ , quickly.

Figure 5.2 Measurement of V, for a p-Channel Device

### · Setup:

Assemble the circuit as shown in Fig. 5.2 using your array. Ensure that both substrate pins (14 and 7) are connected appropriately. All other pins may be left floating. Ensure that the supply is precisely some convenient value (say 10.00 V), by connecting pins 1 and 2 momentarily (and reading the DVM).

### · Measurement:

- Measure the voltage from node A to ground (that is, read the DVM!). Estimate V<sub>g</sub>.

- Repeat the measurement with drain and source interchanged (ie, pin 2 as source and pin 1 as drain).

- c) Use your DVM to measure V<sub>p</sub> of the other p-channel devices having either pins 6 and 13, or 10 and 12, connected as node A, and with pins 11 and 14 joined (with 1 or 2) to the + 10 V supply.

#### \* Tabulation:

Source-pin #, VA, V,.

### · Analysis:

Consider the ease with which you can measure the important device parameter  $V_t$ . Note the degree of device-to-device matching and of device symmetry, you have found.

# E1.2 Measuring the Device Conductivity Parameter

### · Goal:

To find k, quickly.

### · Setup:

Use the circuit shown in Fig. 5.2, the same as in E1.1, above.

### Measurement:

- Short pins 1 and 2 to measure the supply voltage. Set it to some convenient value (eg, 10.00 V).

- Now, with the short removed, measure the voltage at the drain-gate common connection (node A).

- c) Now, shunt the DVM with resistors of 10kΩ or less until the DVM reading lowers by a reasonable amount, say 1 V. Note that a convenient way to do this is to use a (10kΩ) potentiometer, whose set value is measured subsequently with an ohmmeter. Alternatively, a decade resistor box provides a self-calibrated alternative. Of course, just trying various resistors is OK, since the change does not have to be exact, only measurable. Use the relationship i<sub>D</sub> = V2k<sub>p</sub> (v<sub>GS</sub> V<sub>p</sub>)<sup>2</sup>, from Eq. 5.18 in the Text, to find k<sub>p</sub> = k<sub>p</sub>(W/L).

#### \* Tabulation:

VAO. R. VAR.

### · Analysis:

Consider the ease with which, first  $V_t$ , then k are found, using a very simple experimental setup. Note that the relatively complex process used here to measure k, leads to a convenient calculation, but is otherwise not essential. As noted above, a measurement with any (known) resistor allowing a suitable current flow is all that is needed!

### E1.3 Measuring n-Channel Device Parameters

#### · Goal:

To completely characterize an n-channel device, by finding  $V_{in}$  and  $k_n$ , and to do so in a very simple and direct way.

Figure 5.3 Measurement of V, and k for An n-Channel Device

### · Setup:

O Assemble the circuit shown in Fig. 5.3. Notice the relationship to Fig. 5.2. Note that the NMOS substrate is grounded through pin 7.

### · Measurement:

a) First, measure V<sub>m</sub>, almost directly, as the difference between the supply voltage and the DVM reading.

- Then, shunting the DVM by some appropriate resistor, say 1kΩ, find the device voltage, current, and then k<sub>a</sub>.

- · Tabulation:

R, V (with computed  $V_i$ ,  $i_p$ , and  $k_n$ ), for  $R = \infty$  or  $1 \text{ k}\Omega$ .

#### · Analysis:

Consider again the ease with which a large amount of information can be found about a MOS device from a very simple experiment.

• The Amplifier Function We are now going to explore basic amplifier functions, properties and parameters using the circuit of Fig. 5.4. While this is not an appropriate amplifier topology for most applications, it has the advantages in the present context of simplicity with adaptability. The voltage V<sub>1</sub> is a dc supply whose role it is to adjust the dc component of v<sub>GS</sub> and hence the dc value of i<sub>D</sub>. The voltage V<sub>2</sub> is a second dc supply with which one can control the dc value of v<sub>DS</sub>, once the value of I<sub>D</sub> is established. Capacitor C isolates the dc level at node B, but is large enough (compared to the resistance level at B) to represent a short-circuit for signals in the frequency range of interest.

Figure 5.4 A Simple Grounded-Source Amplifier Topology

### E2.1 Device Transconductance

· Goal:

To evaluate device transconductance.

- · Setup:

- Assemble the circuit of Fig. 5.4 using the 345 NFET (the one whose pins are 3,4,5) with substrates connected to ground and V<sub>2</sub> appropriately.

- Measurement: {Use your DVM for steps a) and b) and your oscilloscope otherwise.}

- Adjust the signal generator for zero output. With V<sub>2</sub> = 6 V, adjust V<sub>1</sub> until V<sub>C</sub> = 5 V. Measure V<sub>1</sub> (why not V<sub>B</sub>?).

- b) Apply a I Vpp sine wave at 1 kHz to node I, while displaying the voltages at nodes A and C on your oscilloscope. Use ac coupling on the channel connected to node C (for these early measurements). Find the voltage gain A<sub>ν</sub> = υ<sub>c</sub> / υ<sub>a</sub> from node A to node C. Under the assumption that A<sub>ν</sub> = g<sub>m</sub>R<sub>D</sub>, estimate g<sub>m</sub>.

- · Tabulation:

V1 1c. Up. Uc. Uc/Up. 2m.

#### · Analysis:

Consider how this value of  $g_m$  corresponds to the calculation using Eq. 5.43 in the Text with estimates of  $V_t$  and K you have already made. If you do not have these values, ignore this calculation and carry on.

#### · Measurement:

- c) With an input signal of zero, raise V<sub>2</sub> to +15 V, and then V<sub>1</sub> until V<sub>C</sub> = 5 V. Measure V<sub>1</sub> (but not V<sub>B</sub>!).

- d) Now, with a 1 Vpp sine wave at 1 kHz at node I, display and measure the signals on nodes A and C. What is the voltage gain from node A to node C? Estimate g<sub>m</sub>.

#### · Tabulation:

V1, Ic. Up. Uc. Uchb. Sm.

### \* Analysis:

Consider how the  $g_{ev}$  and bias data you have obtained in this Exploration, can be used to calculate  $V_t$  and k of the transistor you are using. {Hint: Think about Eq. 5.45 and 5.43 of the Text.}

### E2.2 Signal Distortion

### · Goal:

To explore the wave-shape distortion which results with large signals.

#### \* Setup:

Use the circuit of Fig. 5.4 with V<sub>2</sub> = 15 V and V<sub>1</sub> adjusted so that V<sub>C</sub> = 5 V, and a 0.1 Vpp triangle wave at 1 kHz applied to node I.

#### · Measurement:

- a) Measure nodes A and C, on oscilloscope channel A and B, respectively, with channel B set to ac coupling, and channel A for signal inversion. Adjust the channel A position and gain control channel until the two waveforms exactly overlap.<sup>2</sup>

- b) Raise the generator output level, until the input and output waveforms differ by 10% in peak amplitude. {If the signals get too large on the screen, you may need to reduce them using the channel attentuators on both channels.} Note the peak-to-peak amplitude of the waveform at node C.

- c) Switch the node-C channel to dc coupling and measure the dc values of the peaks of the triangle waveform.

### · Analysis:

Consider the nature of the distortion you are seeing: There are two kinds, one a result of the squarelaw device characteristic (see Eq. 5.39 of the Text), and the other due to operation in the triode region. What kind do you see? How could you demonstrate the other kind? {Hint: Consider changing  $V_2$ .}

### THE FEEDBACK-BIAS TOPOLOGY

<sup>&</sup>lt;sup>2</sup> This is a particular kind of channel "normalization" that is very useful in amplifier gain evaluation. See the commentary on "normalization" in Experiment #0.

Our concentration will be on one of the many possible bias techniques that are shown in Fig. 5.39 of the Text, in particular, the one using resistor feedback from drain to gate. There are several reasons for this choice, some practical, some paedogogical: First, this topology allows direct grounding of the source, avoiding the need for a source-bypass capacitor, which must be very large in practice. Second, this topology always guarantees operation of the FBT in the saturation region, independent of FET parameters. Third, it extends relatively gracefully from the discrete version to more integrated ones. Fourth, as we shall see, the idea can be generalized to include load biasing as well. Fifth, the resistor from drain to gate directly embodies the idea of feedback, which, as we shall find, is very very important in practical amplifier designs, although often on a more global scale. Finally, though a large resistor is needed, and resistors (particularly large ones) are costly in an IC environment, its value is quite non-critical, making it relatively easier to create with usual IC technologies.

### E3.1 A CMOS Active - Loaded Amplifier

Figure 5.5 A CMOS Common-Source Amplifier

### · Goal:

To demonstrate the relatively high gain available from an active-loaded CMOS amplifier.

### · Setup:

O Assemble the circuit shown in Fig. 5.5 using Q<sub>2</sub>, Q<sub>3</sub> and Q<sub>4</sub> to provide a constant-current load to Q<sub>1</sub>. Note the substrate connections, as essential!

#### Measurement:

- a) With the supply at 15 V, measure the dc voltages at nodes E and C. Estimate the current in Q<sub>1</sub> and its g<sub>m</sub> using earlier measured data.

- With a 0.1 Vpp triangle wave at 10 kHz applied to node A, display the waveforms at nodes A, C and D. Calculate the gains υ<sub>c</sub>/υ<sub>a</sub>, υ<sub>d</sub>/υ<sub>l</sub>.

#### · Tabulation:

$V_c$ ,  $v_a$ ,  $v_c$ ,  $v_d$ ,  $v_c/v_e$ ,  $v_d/v_e$ .

### · Analysis:

Consider the relatively large gain you find with an active current-source load. How does it compare with a calculation mode using  $g_m$  and  $R_L$ ? Consider the effect of  $r_o$  of Q and  $Q_2$ ? What is the effect of  $C_2$  on amplifier performance? [This is easier to see if you lower the input

frequency somewhat.]

### E3.2 Nonlinear Distortion

### · Goal:

To evaluate the effects of signal size on amplifier performance.

### \* Setup:

Use Fig. 5.5, as in E3.1 above, with a 0.1 Vpp triangle wave at 10 kHz applied at A.

#### \* Measurement:

- a) Superimpose the input and output signals (at A, D) by adjusting the gain of the "node-A" channel appropriately. [Note that you may want to use C as the output node to avoid the frequency dependent effects of C<sub>2</sub>, which tend to "bend" the sides of the triangle wave.}

- b) Now, raise the input amplitude, slowly, noting evidence of nonlinearity, then of clipping. At significant events, shift the probe from node D to note the direct-coupled levels at node C.

### E3.3 Measuring the Input Resistance

### · Goal:

To evaluate the effect on input resistance of the feedback-bias technique.

### · Setup:

Reconsider the circuit of Fig. 5.5, but with a 1 MΩ resistor connected between node A

and the generator at node I.

#### · Measurement:

a) Apply a 0.2 Vpp sine wave at i. Measure the peak-to-peak voltages at nodes Γ, A, C. Estimate the gain v<sub>e</sub> / v<sub>n</sub> and the equivalent input resistance R<sub>in</sub> evaluated to the right of node A.

### · Tabulation:

### · Analysis:

Consider the value of the input resistance you have found. What value did you expect? What happened? [Hint: Think about the fact that the feedback resistor  $R_G$  has  $v_b$  at its left and  $A_v v_b$  at its right!] Is your confidence shaken or reinforced?

I hope that your first experience with MOS Transistors has been MOST enjoyable!

How did you like the idea of active loads? Now you realize that passive loads, like passive people, are rather dull!